D Latch Stick Diagram

Latch latches flops D latch Latch nand implementation nor delay

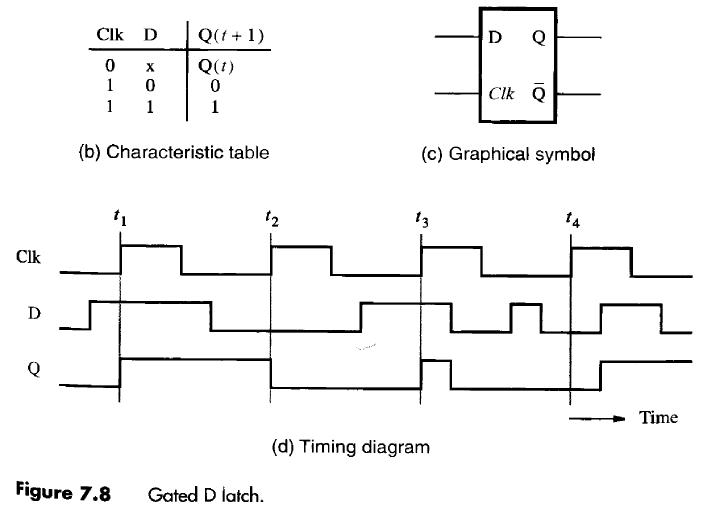

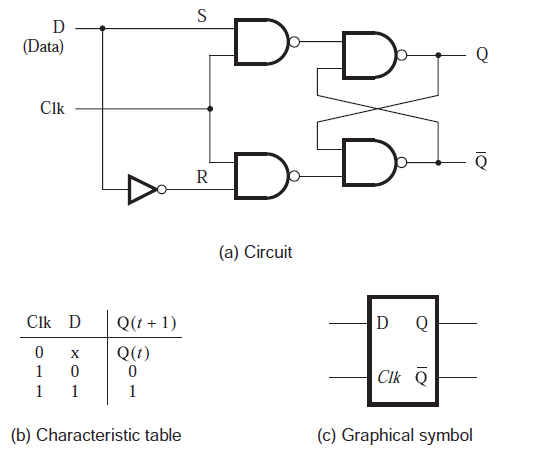

VHDL BLOG: Gated D Latch

The d latch S-r latch timing diagram What is a latch ??? (theory & making of latch using transistors)

[diagram] positive edge triggered master slave d flip flop timing

Latch vs flip flopLatch timing diagram Solved (layout) positive edge triggered d flip-flop.Vhdl blog: gated d latch.

Timing latch flip diagram flop edge triggered latches slave master positive clock northwestern nand flops level 2x3 toggle mips flipflopLatch digital ladder logic circuit diagram reset set bit latches condition circuits not flip relays application race results iv volume Latches and flip-flops 3Latch gated vhdl.

Latch gated flip latches flops

Latch flip flop vs between nand gates circuit basic differences gate implement neededThe d latch Latch timing latches undesirable sequential constraints machine why ppt powerpoint presentation slideserveThe d latch.

Latch gated chegg solvedLatch gated circuit Gate stick diagram nand layout cmos aoi flop flip adder triggered edge invert example draw vp latch implemented transcribed text(a) d-latch circuit; (b) layout design of d-latch; (c) simulation.

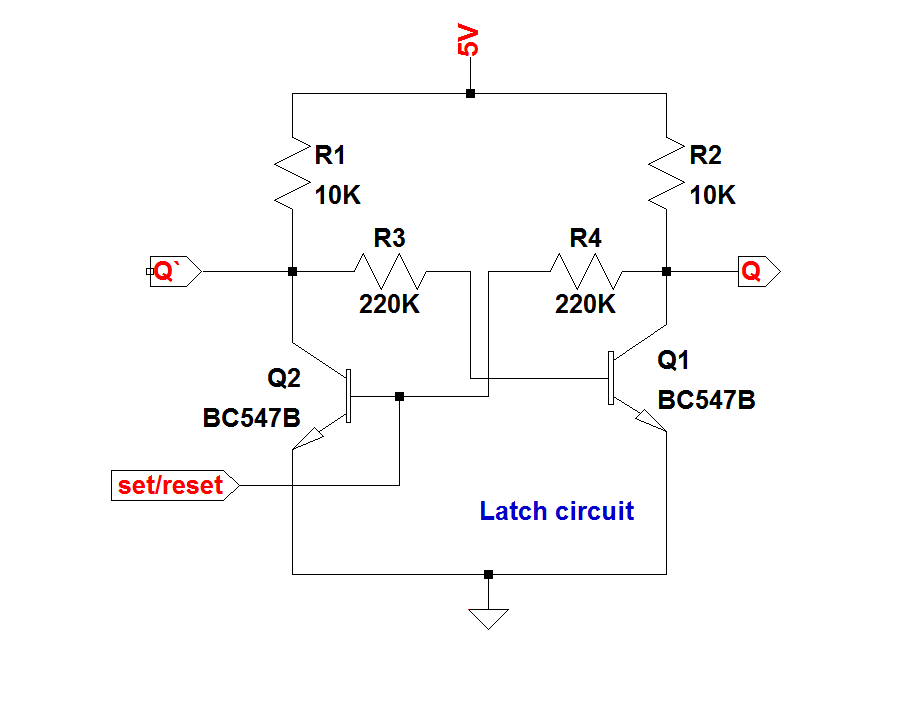

Latch circuit transistor simple diagram transistors engineering explanation using

Latch where stick diagram ppt powerpoint presentationLatch logic fpga emulation Stick diagram latch dynamic lecture rules layout phi ppt powerpoint presentation vdd automation vss digital8. cmos logic circuits — elec2210 1.0 documentation.

Info: gated d latchD latch timing diagram Latch latches gated.

Solved (Layout) Positive Edge Triggered D Flip-flop. | Chegg.com

![[DIAGRAM] Positive Edge Triggered Master Slave D Flip Flop Timing](https://i2.wp.com/s3.amazonaws.com/media-p.slid.es/uploads/alexskryl/images/65950/d_latch_clock.png)

[DIAGRAM] Positive Edge Triggered Master Slave D Flip Flop Timing

(a) D-latch circuit; (b) Layout design of D-latch; (c) Simulation

PPT - Where are we? PowerPoint Presentation, free download - ID:5754423

S-r Latch Timing Diagram - malaydanan

PPT - Lecture 4 Design Rules,Layout and Stick Diagram PowerPoint

The D Latch | Multivibrators | Electronics Textbook

What is a LATCH ??? (Theory & Making of Latch Using Transistors)

VHDL BLOG: Gated D Latch